## ALL RIGHTS RESERVED BY FRED MUNDELL and FUNDAMENTAL DESIGNS LTD.

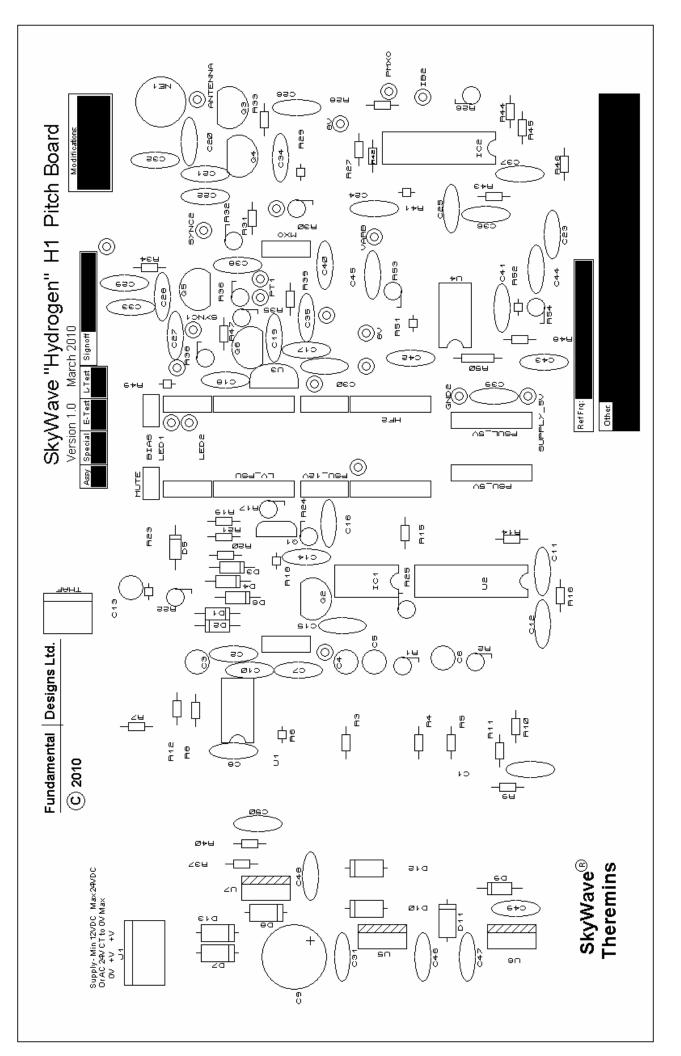

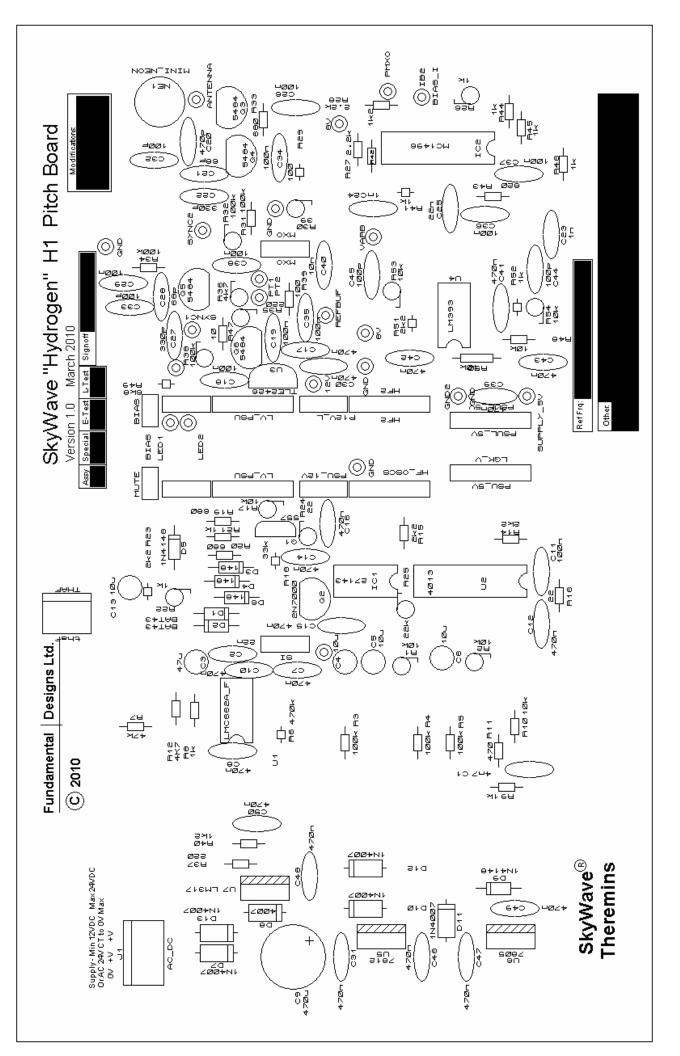

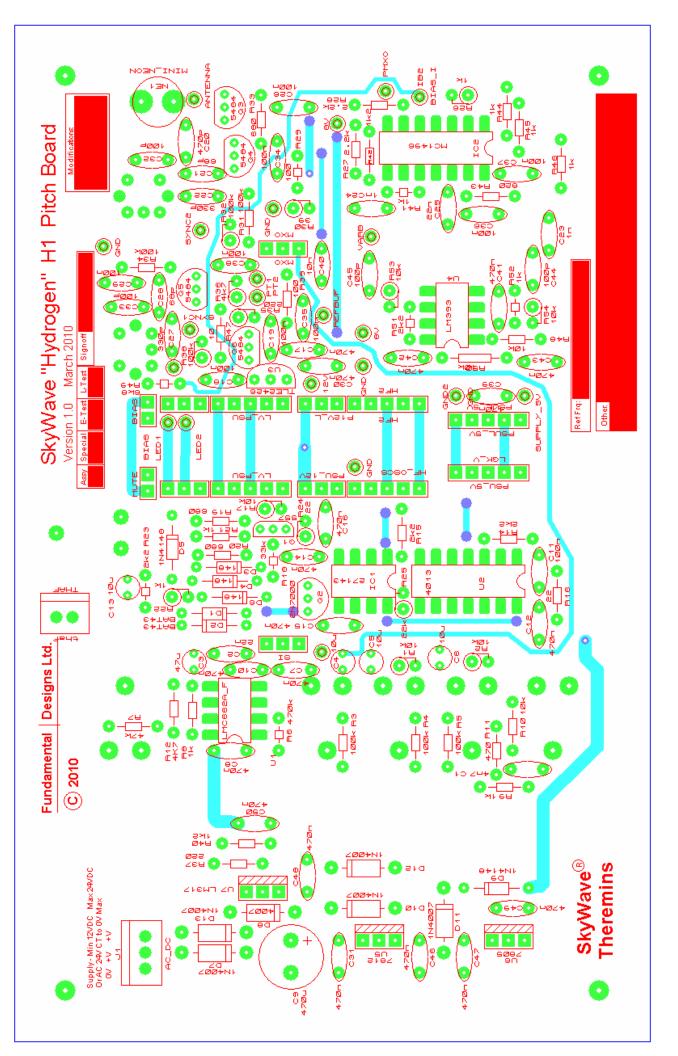

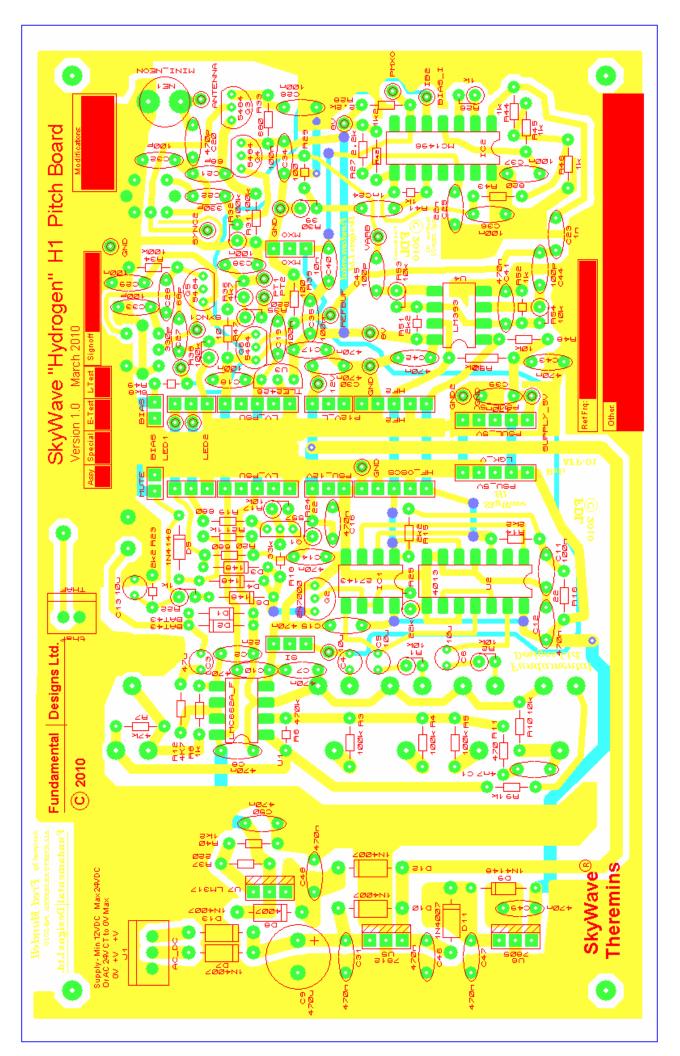

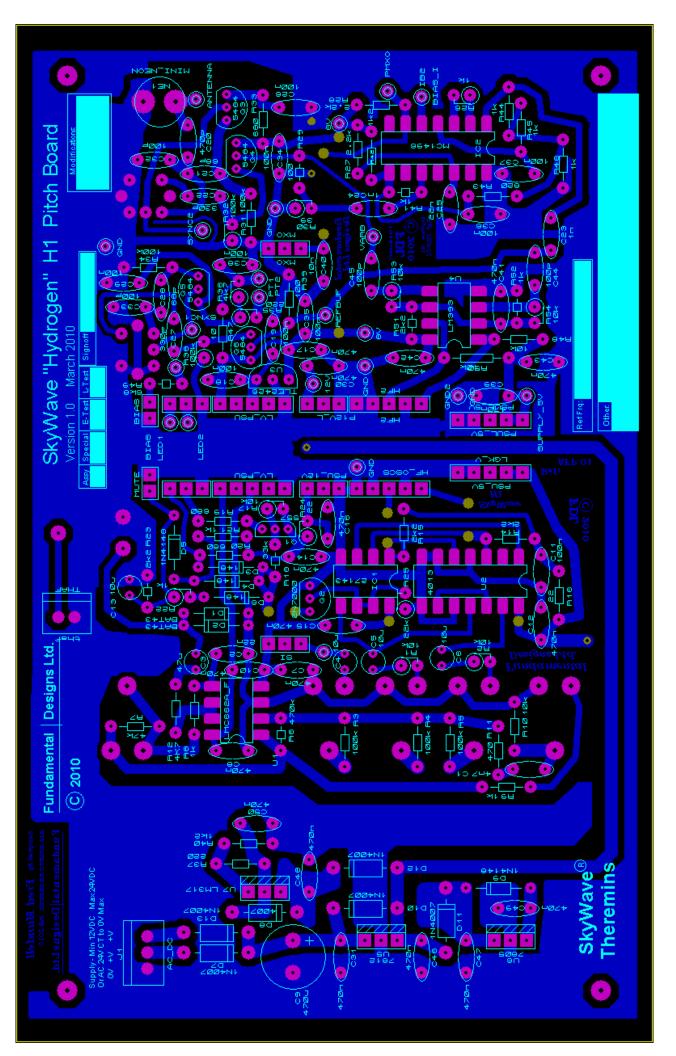

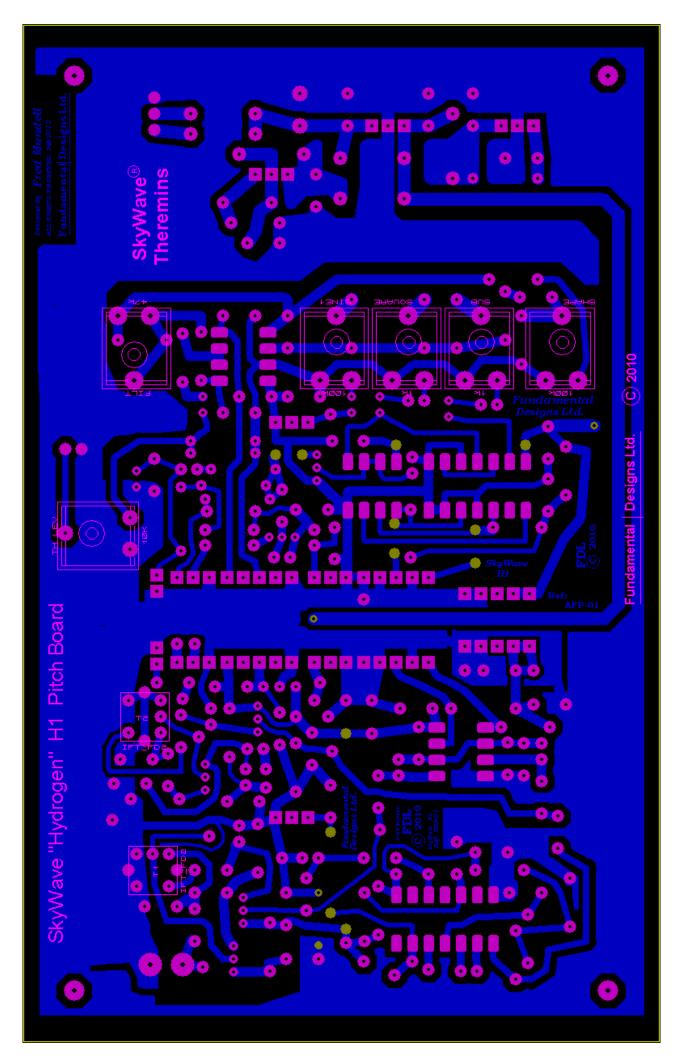

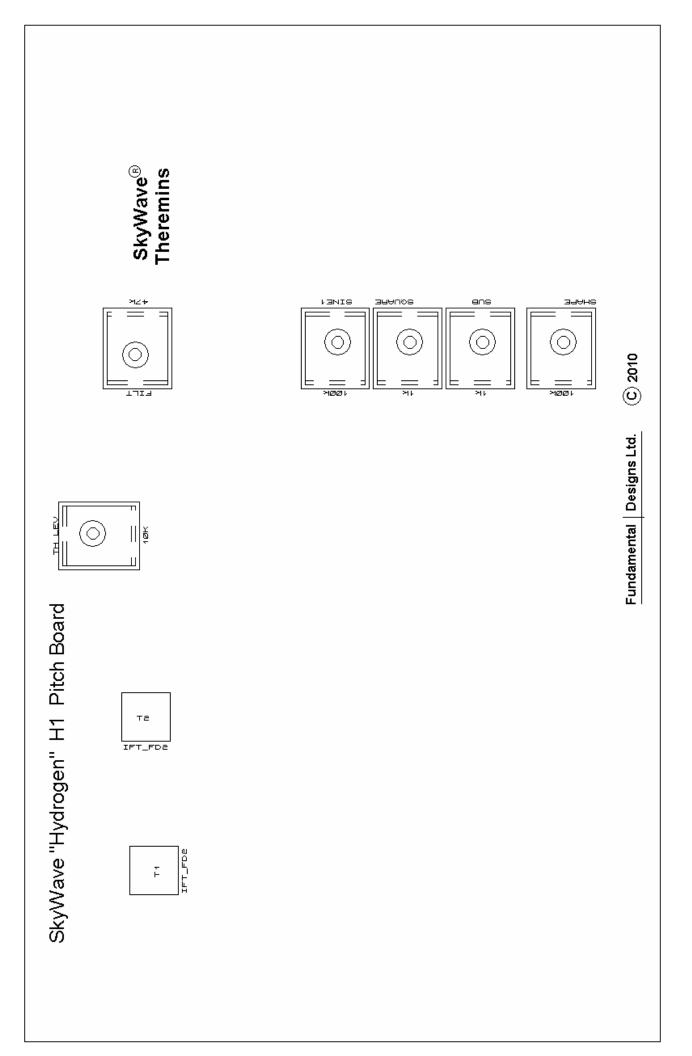

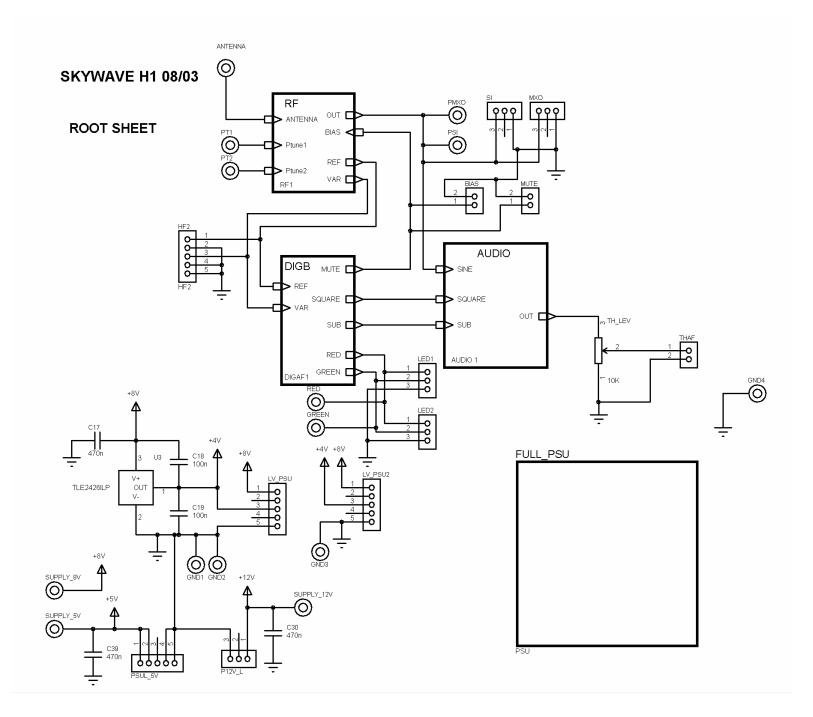

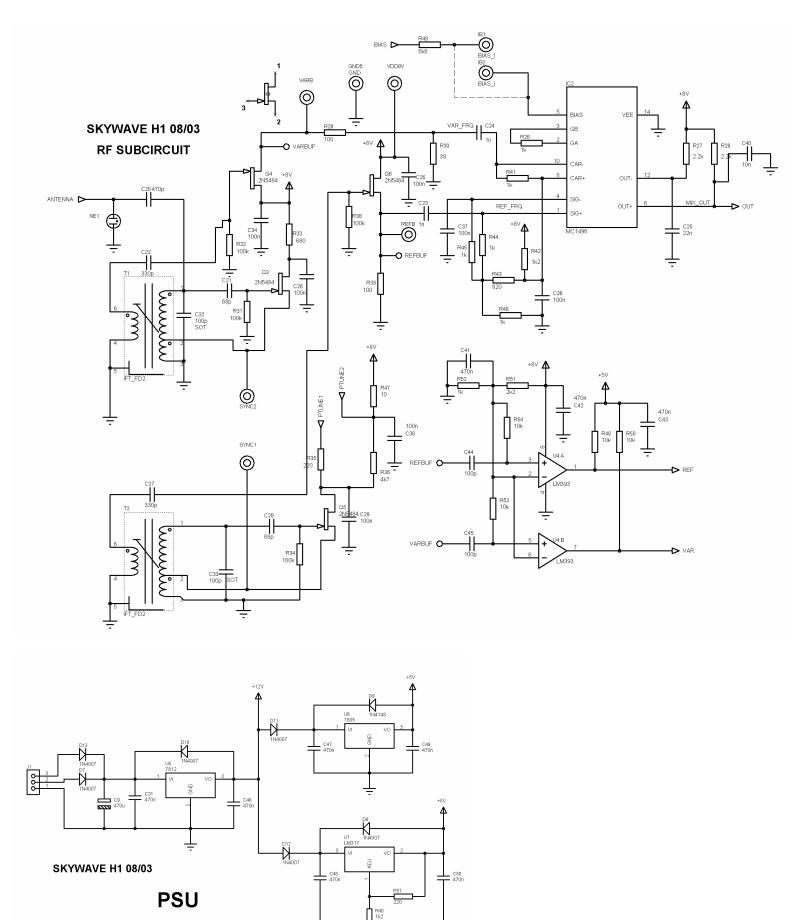

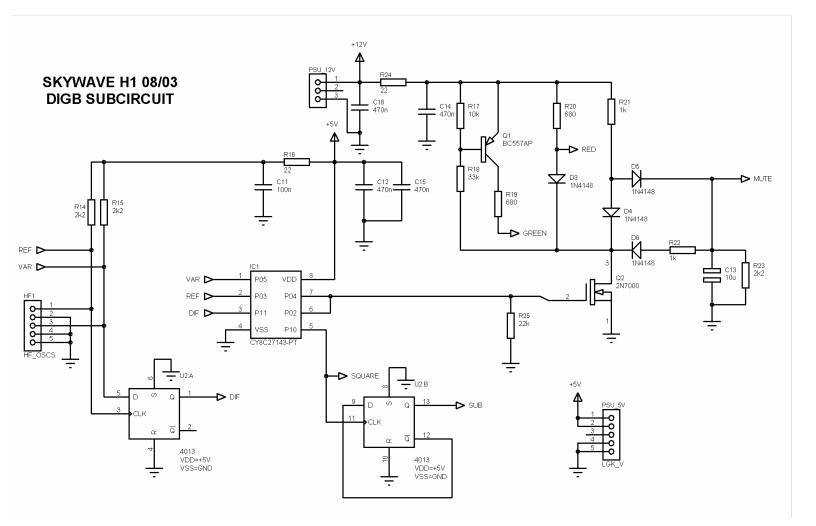

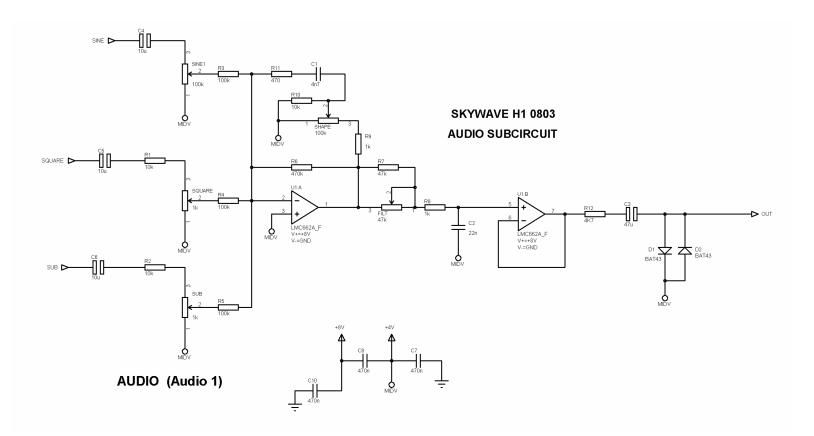

These schematics / code / layouts are for the Skywave H1 Pitch-only "Theremin". 16 of these were built and operated in the Royal Festival Hall (South-bank arts centre) for 10 days in 2010.

These notes are being published without any permission for any entity to copy, use or manufacture these instruments – The ONLY permission given is for individuals to use this content for educational purposes, or for construction of ONE instrument based on the information given here, FOR THEIR OWN USE ONLY.

NO warranty of ANY KIND is given for the content herein. I will not undertake ANY correspondence regarding this content unless a donation of not less than £10 is made to <u>http://www.streetkidsrescue.org/</u> prior to contacting me – When donating, please insert the words Skywave Theremin in the comment field – I will then receive notification of your email address and know that you have paid.

÷

I can provide a pre-programmed H1 PSoC for £15. Email : <u>fred@fundes.co.uk</u> All code and details required to copy this part are provided below, and PSoC designer is available from Cypress FOC.

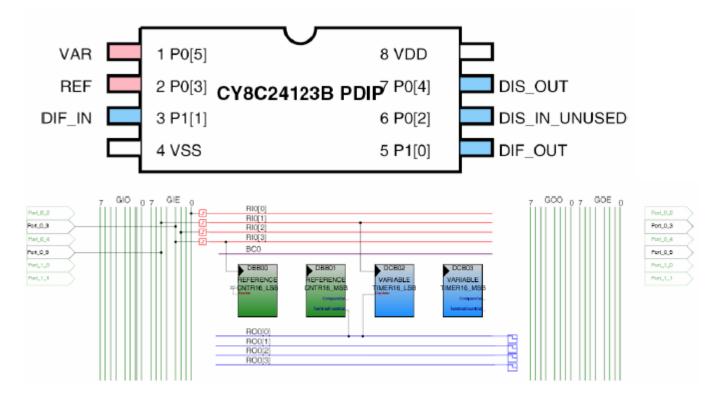

Configuration of PSoC CY8C27143: IC 1

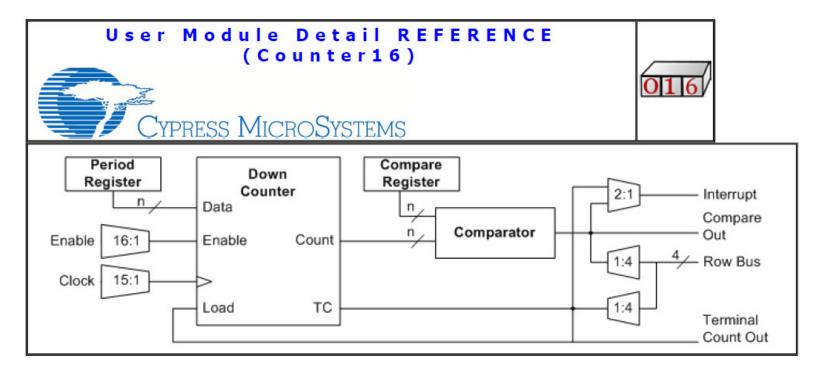

Extremely simple – Frequencies of reference and variable oscillators are compared using the CTR16 and TIMER16 UM's, The state is computed in the UM's ISR's (Interrupt Service Routines) and these return a flag (Null) which is polled by the main routine – If Variable oscillator frequency exceeds Reference oscillator frequency, Null is set, P0:4 is driven high, and the input on P1:1 is not passed through to P1:0

When Variable oscillator frequency < Reference oscillator frequency, Null is cleared, P0:4 is driven low, and the input on P1:1 is passed through to P1:0

It should be noted that this instrument has both analogue and "digital" signal paths, the "digital" signal path is disconnected by this PSoC when nulling (silencing) is required, the analogue signal is nulled at the mixer via the output from P0:4 (which also drives the LED).

## Signal Pin Table (sky\_h1\_v2)

| Pin# | Port  | Label         | Select         | Drive       | Interrupt  |

|------|-------|---------------|----------------|-------------|------------|

| 1    | P0[5] | VAR           | GlobalInEven_5 | High Z      | DisableInt |

| 2    | P0[3] | REF           | GlobalInEven_3 | High Z      | DisableInt |

| 3    | P1[1] | DIF_IN        | StdCPU         | High Z      | DisableInt |

| 4    | VSS   |               |                |             |            |

| 5    | P1[0] | DIF_OUT       | StdCPU         | Strong Slow | DisableInt |

| 6    | P0[2] | DIS_IN_UNUSED | StdCPU         | High Z      | DisableInt |

| 7    | P0[4] | DIS_OUT       | StdCPU         | Strong Slow | DisableInt |

| 8    | VDD   |               |                |             |            |

| Name                                | Value             |

|-------------------------------------|-------------------|

| 32K_Select                          | Internal          |

| A_Buff_Power                        | Low               |

| Analog Power                        | All Off           |

| CPU_Clock                           | SysClk/1          |

| LVDThrottleBack                     | Disable           |

| Op-Amp Bias                         | Low               |

| PLL_Mode                            | Disable           |

| Power Setting [ Vcc / SysClk freq ] | 5.0V / 24MHz      |

| Ref Mux                             | (Vdd/2)+/-BandGap |

| Sleep_Timer                         | 512_Hz            |

| SwitchModePump                      | OFF               |

| SysClk*2 Disable                    | Yes               |

| Trip Voltage [LVD (SMP)]            | 4.81V (5.00V)     |

| VC1= SysClk/N                       | 1                 |

| VC2= VC1/N                          | 1                 |

| VC3 Divider                         | 1                 |

| VC3 Source                          | SysClk/1          |

| Watchdog Enable                     | Disable           |

## Parameters

| Parameters       | Value          |

|------------------|----------------|

| Clock            | Row_0_Input_3  |

| ClockSync        | Unsynchronized |

| CompareOut       | None           |

| CompareType      | Less Than      |

| CompareValue     | 0000           |

| Enable           | High           |

| IntDispatchMode  | ActiveStatus   |

| InterruptAPI     | Enable         |

| InterruptType    | Terminal Count |

| InvertEnable     | Normal         |

| Period           | 65535          |

| TerminalCountOut | Row_0_Output_0 |

Blocks

| DIUCKS                                                             |                                                                        |                                      |                   |  |  |

|--------------------------------------------------------------------|------------------------------------------------------------------------|--------------------------------------|-------------------|--|--|

| Block                                                              | Туре                                                                   | Location                             | ]                 |  |  |

| CNTR16_LSB                                                         | DIGITAL                                                                | 0                                    |                   |  |  |

| Registers                                                          | Name                                                                   | Address                              | Value             |  |  |

| CONTROL_0                                                          | DBB00CR0                                                               | 23                                   | 0                 |  |  |

| DATA_0                                                             | DBB00DR0                                                               | 20                                   | 0                 |  |  |

| DATA_1                                                             | DBB00DR1                                                               | 21                                   | ff                |  |  |

| DATA_2                                                             | DBB00DR2                                                               | 22                                   | 0                 |  |  |

| DIG_BasicFunction                                                  | DBB00FN                                                                | 120                                  | 11                |  |  |

| DIG_Input                                                          | DBB00IN                                                                | 121                                  | 1f                |  |  |

| DIG_Output                                                         | DBB00OU                                                                | 122                                  | 0                 |  |  |

|                                                                    |                                                                        |                                      |                   |  |  |

| Block                                                              | Туре                                                                   | Location                             | ]                 |  |  |

| Block<br>CNTR16_MSB                                                | Type<br>Digital                                                        | Location<br>1                        |                   |  |  |

|                                                                    |                                                                        | Location<br>1<br>Address             | Value             |  |  |

| CNTR16_MSB                                                         | DIGITAL                                                                | 1                                    | <b>Value</b><br>0 |  |  |

| CNTR16_MSB<br>Registers                                            | DIGITAL<br>Name                                                        | 1<br>Address                         |                   |  |  |

| CNTR16_MSB<br>Registers<br>CONTROL_0                               | DIGITAL<br>Name<br>DBB01CR0                                            | 1<br><b>Address</b><br>27            | 0                 |  |  |

| CNTR16_MSB<br>Registers<br>CONTROL_0<br>DATA_0                     | DIGITAL<br>Name<br>DBB01CR0<br>DBB01DR0                                | 1<br><b>Address</b><br>27<br>24      | 0<br>0            |  |  |

| CNTR16_MSB<br><b>Registers</b><br>CONTROL_0<br>DATA_0<br>DATA_1    | DIGITAL<br><b>Name</b><br>DBB01CR0<br>DBB01DR0<br>DBB01DR1             | 1<br>Address<br>27<br>24<br>25       | 0<br>0<br>ff      |  |  |

| CNTR16_MSB<br>Registers<br>CONTROL_0<br>DATA_0<br>DATA_1<br>DATA_2 | DIGITAL<br><b>Name</b><br>DBB01CR0<br>DBB01DR0<br>DBB01DR1<br>DBB01DR2 | 1<br>Address<br>27<br>24<br>25<br>26 | 0<br>0<br>ff<br>0 |  |  |

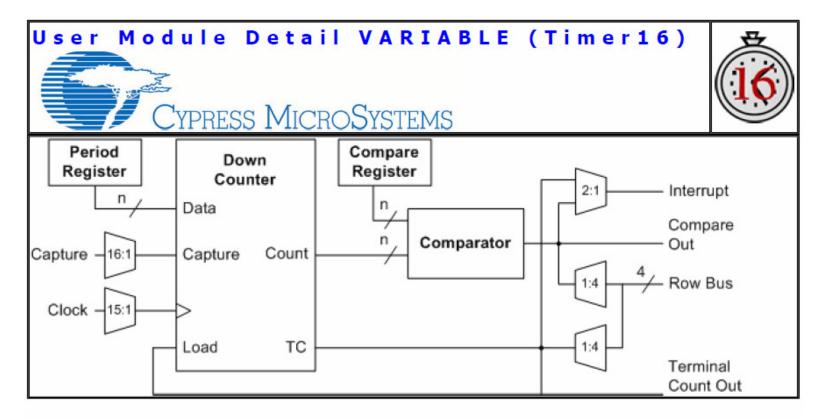

## Parameters

| Parameters       | Value              |

|------------------|--------------------|

| Capture          | Row_0_Output_0     |

| Clock            | Row_0_Input_1      |

| ClockSync        | Unsynchronized     |

| CompareOut       | None               |

| CompareType      | Less Than Or Equal |

| CompareValue     | 0000               |

| IntDispatchMode  | ActiveStatus       |

| InterruptAPI     | Enable             |

| InterruptType    | Terminal Count     |

| InvertCapture    | Normal             |

| Period           | 65535              |

| TC_PulseWidth    | Full Clock         |

| TerminalCountOut | None               |

|                   | Bloc     | : k s    |       |

|-------------------|----------|----------|-------|

| Block             | Туре     | Location |       |

| TIMER16_LSB       | DIGITAL  | 2        |       |

| Registers         | Name     | Address  | Value |

| CONTROL_0         | DCB02CR0 | 2b       | 0     |

| DATA_0            | DCB02DR0 | 28       | 0     |

| DATA_1            | DCB02DR1 | 29       | ff    |

| DATA_2            | DCB02DR2 | 2a       | 0     |

| DIG_BasicFunction | DCB02FN  | 128      | 0     |

| DIG_Input         | DCB02IN  | 129      | 8d    |

| DIG_Output        | DCB02OU  | 12a      | 0     |

| Block             | Туре     | Location |       |

| TIMER16_MSB       | DIGITAL  | 3        |       |

| Registers         | Name     | Address  | Value |

| CONTROL_0         | DCB03CR0 | 2f       | 4     |

| DATA_0            | DCB03DR0 | 2c       | 0     |

| DATA_1            | DCB03DR1 | 2d       | ff    |

| DATA_2            | DCB03DR2 | 2e       | 0     |

| DIG_BasicFunction | DCB03FN  | 12c      | 20    |

| DIG_Input         | DCB03IN  | 12d      | 3d    |

| DIG_Output        | DCB03OU  | 12e      | 0     |

| Global Register Values (sky_h1_v2)          |           |         |       |  |  |

|---------------------------------------------|-----------|---------|-------|--|--|

| Register                                    | Name      | Address | Value |  |  |

| AnalogClockSelect1                          | CLK_CR1   | 161     | 0     |  |  |

| AnalogClockSelect2                          | CLK_CR2   | 169     | 0     |  |  |

| AnalogColumnClockSelect                     | CLK_CR0   | 160     | 0     |  |  |

| AnalogColumnInputSelect                     | AMX_IN    | 60      | 9     |  |  |

| AnalogComparatorControl1                    | CMP_CR1   | 66      | 0     |  |  |

| AnalogIOControl_0                           | ABF_CR0   | 162     | 0     |  |  |

| AnalogLUTControl0                           | ALT_CR0   | 167     | 33    |  |  |

| AnalogLUTControl1                           | ALT_CR1   | 168     | 0     |  |  |

| AnalogModulatorControl_0                    | AMD_CR0   | 163     | 0     |  |  |

| AnalogModulatorControl_1                    | AMD_CR1   | 166     | 0     |  |  |

| AnalogReferenceControl                      | ARF_CR    | 63      | 0     |  |  |

| AnalogSyncControl                           | ASY_CR    | 65      | 0     |  |  |

| DecimatorControl_0                          | DEC_CR0   | e6      | 0     |  |  |

| DecimatorControl_1                          | DEC_CR1   | e7      | 0     |  |  |

| GlobalDigitalInterconnect_Drive_Even_Input  | GDI_E_IN  | 1d1     | 0     |  |  |

| GlobalDigitalInterconnect_Drive_Even_Output | GDI_E_OU  | 1d3     | 0     |  |  |

| GlobalDigitalInterconnect_Drive_Odd_Input   | GDI_O_IN  | 1d0     | 0     |  |  |

| GlobalDigitalInterconnect_Drive_Odd_Output  | GDI_O_OU  | 1d2     | 0     |  |  |

| I2CConfig                                   | I2CCFG    | d6      | 0     |  |  |

| OscillatorControl_1                         | OSC_CR1   | 1e1     | 0     |  |  |

| OscillatorControl_2                         | OSC_CR2   | 1e2     | 1     |  |  |

| OscillatorControl_3                         | OSC_CR3   | 1df     | 0     |  |  |

| OscillatorControl_4                         | OSC_CR4   | 1de     | 0     |  |  |

| OscillatorGlobalBusEnableControl            | OSC_GO_EN | 1dd     | 0     |  |  |

| Port_0_DriveMode_0                          | PRT0DM0   | 100     | 10    |  |  |

| Port_0_DriveMode_1   | PRT0DM1  | 101 | 2c |

|----------------------|----------|-----|----|

| Port_0_DriveMode_2   | PRT0DM2  | 3   | 10 |

| Port_0_GlobalSelect  | PRT0GS   | 2   | 28 |

| Port_0_IntCtrl_0     | PRT0IC0  | 102 | 0  |

| Port_0_IntCtrl_1     | PRT0IC1  | 103 | 0  |

| Port_0_IntEn         | PRTOIE   | 1   | 0  |

| Port_1_DriveMode_0   | PRT1DM0  | 104 | 1  |

| Port_1_DriveMode_1   | PRT1DM1  | 105 | 2  |

| Port_1_DriveMode_2   | PRT1DM2  | 7   | 1  |

| Port_1_GlobalSelect  | PRT1GS   | 6   | 0  |

| Port_1_IntCtrl_0     | PRT1IC0  | 106 | 0  |

| Port_1_IntCtrl_1     | PRT1IC1  | 107 | 0  |

| Port_1_IntEn         | PRT1IE   | 5   | 0  |

| Port_2_DriveMode_0   | PRT2DM0  | 108 | 0  |

| Port_2_DriveMode_1   | PRT2DM1  | 109 | 0  |

| Port_2_DriveMode_2   | PRT2DM2  | b   | 0  |

| Port_2_GlobalSelect  | PRT2GS   | a   | 0  |

| Port_2_IntCtrl_0     | PRT2IC0  | 10a | 0  |

| Port_2_IntCtrl_1     | PRT2IC1  | 10b | 0  |

| Port_2_IntEn         | PRT2IE   | 9   | 0  |

| Row_0_InputMux       | RDI0RI   | b0  | 4  |

| Row_0_InputSync      | RDI0SYN  | b1  | 0  |

| Row_0_LogicInputAMux | RDI0IS   | b2  | 0  |

| Row_0_LogicSelect_0  | RDI0LT0  | b3  | 33 |

| Row_0_LogicSelect_1  | RDI0LT1  | b4  | 33 |

| Row_0_OutputDrive_0  | RDI0SRO0 | b5  | 0  |

| Row_0_OutputDrive_1  | RDI0SRO1 | b6  | 0  |

//-----// C main line

#include <m8c.h> // part specific constants and macros

#include "PSoCAPI.h" // PSoC API definitions for all User Modules

unsigned int captured; unsigned int last\_captured; unsigned int calculated; unsigned int temp; unsigned char ovflow; unsigned char nullctr; unsigned char null;

```

#define M_READ_DIF PRT1DR&0x02

#define SET_DIF PRT1DR=1

#define CLR_DIF PRT1DR=0

#define CLR_NULL_to_LOW PRT0DR=0

#define SET_NULL_to_HIGH PRT0DR=0x10

```

```

#define REFTICKS 32000

```

void main()

{

```

REFERENCE_WritePeriod(REFTICKS);

VARIABLE_WritePeriod(0xFFFF);

last_captured = 0xFFFF;

```

REFERENCE\_EnableInt(); VARIABLE\_EnableInt();

M8C\_EnableGInt;

```

REFERENCE_Start();

VARIABLE_Start();

while(1)

{

if(null==0)

{

if(M_READ_DIF)

SET_DIF;

else CLR_DIF;

}

}

}

//====

_____

=

#pragma interrupt_handler REFERENCE_ISR

void REFERENCE_ISR(void)

{

captured = VARIABLE_wReadCompareValue();

//-----

if(ovflow < 2)

{

ovflow = 0;

//-----

if(captured > last_captured)

ł

calculated = last_captured;

temp = 0xFFFF - captured;

calculated = calculated+temp;

if(calculated >= REFTICKS)

```

```

ł

if(nullctr < 2)

nullctr++;

}

else if(nullctr > 0)

nullctr--;

}

//---

-----

else{

calculated = (last_captured - captured);

if(calculated >= REFTICKS)

{

if (null ctr < 2)

nullctr++;

}

else if(nullctr > 0)

nullctr--;

}

//-----

if(nullctr == 2)

{

null = 1;

SET_NULL_to_HIGH;

}

else if(nullctr == 0)

{

null = 0;

CLR_NULL_to_LOW;

}

//-----

_____

}

else{

// ERROR HANDLER

if (null ctr < 2)

nullctr++;

if(nullctr == 2)

{

null = 1;

SET_NULL_to_HIGH;

}

}

last_captured = captured;

ovflow = 0;

}

//=

_____

=

#pragma interrupt_handler VARIABLE_ISR

void VARIABLE_ISR(void)

{

ovflow++;

}

```