"t would be you starring in the latter role! ;-)"

Quite possibly - But there are other engineers who do likewise..

The forum which has most impressed me in this regard is the LT-Spice forum - Some of the Engineers there have patience WAY beyond anything I could muster - Simulation can throw up issues that are difficult to debug, and a poorly designed / drafted schematic thrown into a simulator often results in no clues about the problem, just a "convergence error".

Hobbyists will present the most impossible circuits and get talked through the required changes, and advised on things like setting initial conditions - the engineers really love LT-Spice and are passionate about getting people "into it" - And I think it takes this kind of passion to motivate people to actually "give up" hours of their life with no monetary return.. Some irrational passion (like the passion to educate or the passion to share your passion ;-) is required to overcome sanity!

And I never really "contribute" in that forum - not because I dont want to.. At times I feel drawn to, particularly if I feel I could sort the problem out - But I dont - Simply because I know there are engineers there who are willing to help, have greater knowledge than me if things got complex (particularly relating to LT Spice itself, as my expierience is far greater in other simulation packages), and have FAR more patience than I have.. I only participate when I need help. Moderation there is severe and instant - Any troll or time-waster is booted into oblivion before they can blink, and the forum is efficient and constructive, with new simulation models being created, tested, and added to an extensive library frequently - All the required documentation and version managment is in place - its an example of how an open collaboration should be run.

Fred.

Update:

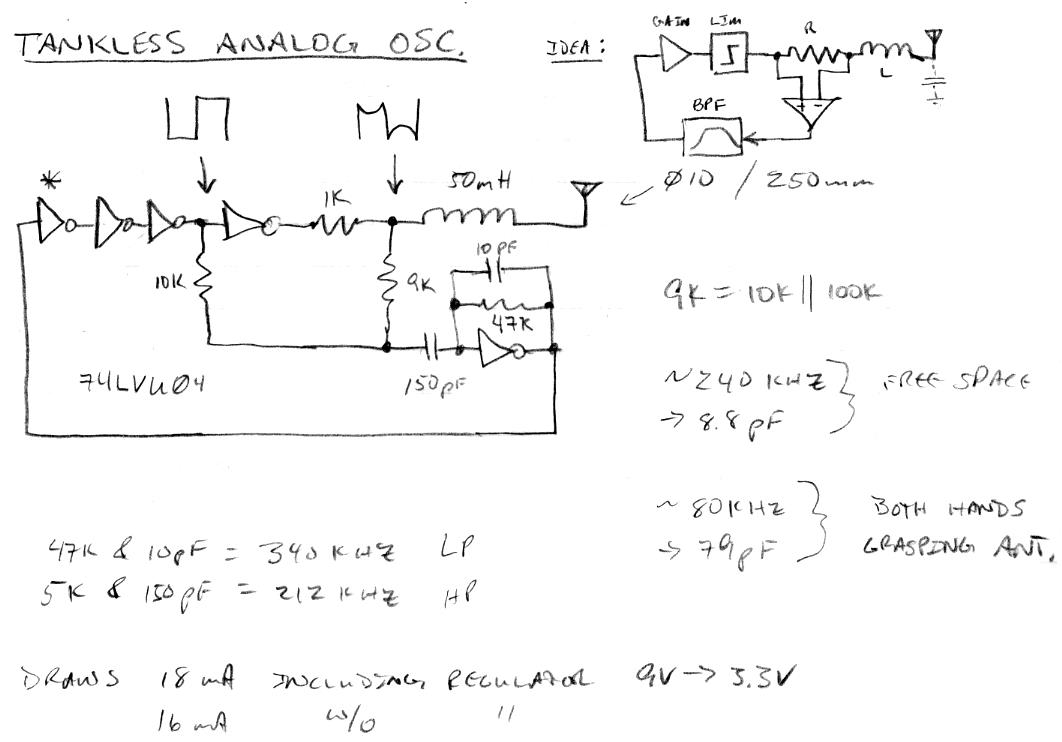

The design for the switched capacitor tuning on the drive side is lovely in theory - runs a treat when using Spice primitive switches.. But theres a big problem I should have seen way back from the waveforms, but just didnt notice...

The problem is that there can be a high voltage across the capacitors when the switch is open - this voltage cannot be clamped as its derived from coupling through the other capacitor or direct from the inductor, and clamping it attenuates the drive signal..

So (from my simulations, giving a reasonable antenna voltage of 80V P-P) the switch must handle about +/- 20V.. The 4066 or 4053 just aint going to cope with that ;-) SSR's and opto's are just not fast enough, so it looks like the only place to implement switched capacitor tuning is at the input, using capacitive potential divider.. and this also has its problems.

Going to look at some fast isolated MOSFET drive IC's and see if I can find one that doesnt have a load of undervoltage detection circuitry and the like - these are the only parts I can find with fast enough switching times and isolation - otherwise its going to need to be a redesign of the output stage using discrete transistors to incorporate the PWM and capacitor switching / voltages etc..

I think I might just give up on this and go back to some other tuning method.

The oscillator still runs and tunes if I clamp the voltages, but a 20kHz frequency (PWM) sweep alters the antenna voltage from about 16V P-P to 80V P-P .. below 16V the oscillator goes unstable anyway.. Using "unreal" switches the whole thing behaves beautifully with stable 80V P-P on the antenna over a 20+ kHz range, but I cannot find a supplier of these unobtanium switches ;-)

I am moving back towards thinking that for MY design a parallel resonant oscillator, perhaps with transformer coupled antenna, is so much easier to tune that I shouldnt spend much more time on this series resonant oscillator.. Oh, I can see the beauty in this oscillator, and for what you are doing Dewster, its ideal... But there comes a time when going back to what one knows and has expierience of - even if its imperfect - might be the wisest option.