"...so when the XOR output is high, you get 0xFF into the HPF, and when the XOR output is low you get 0x00 into the HPF. ... (Actually, I got that wrong.. its a bunch of XORs and a signed result going to the HPF)" - FredM

Yes. If you flip the MSB you get signed, so signed or unsigned is rather trivial / arbitrary. I picked signed so that the thresholding and accumulator initialization is conceptually simpler (@ zero rather than 1/2 the max, though both are just the MSB).

Gates are mainly for human convenience as the tool blends it all together and boils it back down to LUTs. This is what I really like about HDL programming: all the tedious Karnaugh mapping and state machine state assignment and reduction and decoding is done automatically and 99% of the time much better than I can do (particularly from a global perspective). One should be aware of this stuff, but much of what we spent months slaving over in school is otherwise rather moot. (I remember finding BJT bias points to 3 decimal places via iteration, something one would never do in real life because device parameters tend to be terribly sloppy.)

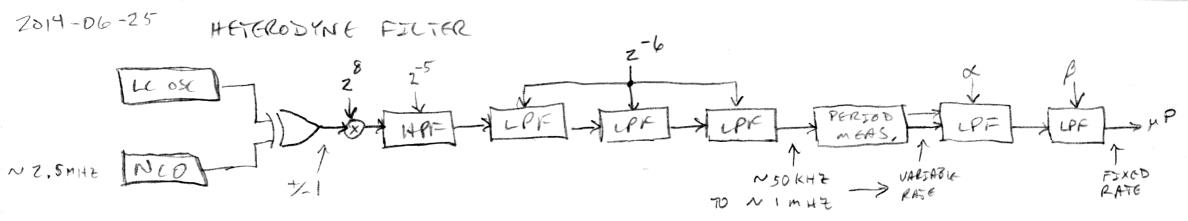

"In terms of FPGA implementation, everything (except LCO) on the diagram is in the FPGA, with only the fixed-rate data from LPF b going to the processor - so there is no processor intervention (?) and you get all the advantages of heterodyning with none of the peripheral analogue hardware..

Real neat, real tidy, huge potential for tweaking without changing components.. You have an NCO that can presumably be adjusted as required."

It seems to work quite well (in simulation) over a large range (~10kHz to ~1.3MHz). The processor will have to get involved in setting the NCO frequency.

Playing with it a bit more this morning the initial multiplication should perhaps be 2^9 to get better resolution at lower frequencies, though of course putting it in HW will be the true test. I'm also thinking the variable rate filter could be second order, and the final fixed rate filter perhaps dispensed with. Have the processor sample it at 50kHz or so, which would give 400 instructions for the thread (running at 20MHz) to do something with the sample like more sophisticated LPF and perhaps 50/60Hz high Q notch.

I've done this kind of circuit in the past for products, but with no heterodyning, and with a single LPF after the period measurement, to measure the "frequency" deviation of an input (actually period deviation, but the two are quite close for small deviations about nominal).

"Verilog ++ or whatever..."

I can't believe they changed the name to SystemVerilog when it's really just an update to Verilog and not a new language at all. The name change is what kept me away from SV - that, and the way SV is "sold" as a primarily for verification and not synthesis so much, which is also quite deceptive. And this is my field! Gaaa!