I dont know how to reference what the simulations show against Fourier or Laplace, or do the maths by hand that the simulation is effectively doing, unseen, for me..

All I know is what I see - and it makes sense at a visual / intuitive level.

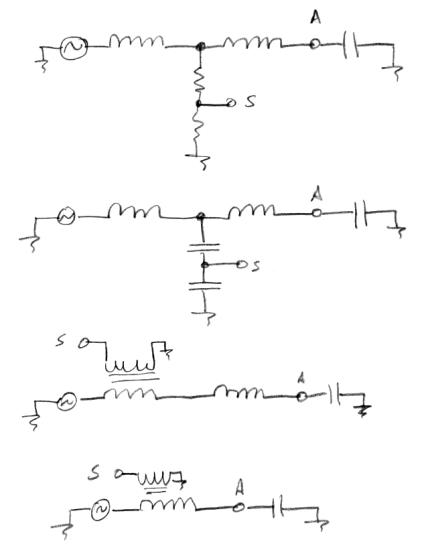

If I operate the PWM over a complete cycle (as in, PWM frequency = MO frequency) there are weird results (dont forget, with the PWM high I am effectively reducing the C in series with the L) - at 50:50, the resulting distortion of the waveform is most extreme (0ne half cycle is operating at the extreme difference in C to the other 1/2 cycle) - The distortion reduces as the PW increases or decreases from 50% - to me it makes sense.. oh, it does "control" the frequency - lowest frequency is when the PWM is low, highest when its high)

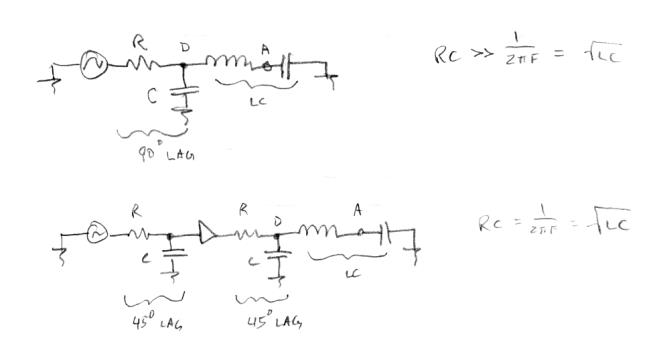

If I operate the PWM at twice the MO frequency, each 1/2 cycle sees the same agregated (switched) capacitance in series with the L for each 1/2 cycle, and at the the antenna there is little distortion.

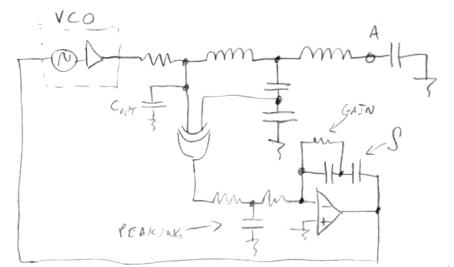

As the C which is being switched (effectively shorted when the PWM is high) is at the drive side, the voltage across it at any time is low - With my latest simulations I have the drive directly coupled to this switched C, followed by a couple of clamping diodes, followed by a 220R resistor, followed by the inductor, followed by a capacitor to ground (the antenna) - and it all seems to behave - I can change the frequency by changing the PWM (using a simple SQW/Pulse SPICE generator component), and distortion is not excessive.

But I havent done extensive examinations, havent run full FFT on the antenna waveforms for any but a few spot checks - I am busy trying to get the loop to work - I have this running a bit, but have devised a somewhat strange frequency / phase detector and rather special PWM circuit - I was too ambitious, should have started simple and expanded - but I only ran one extremely crude PLL simulation, never took enough tests, before I made thing complicated -- If I dont have a breakthrough soon I will need to go back to the earlier PLL simulation and work up from there..

Fred.

* I have needed to adjust the simulation to avoid convergence errors - it only works quite close to setting beyond which I do not trust the results - just within believable parameter boundaries, but not with the accuracy that gives me a lot of confidence.