Pitch and Volume Latency Tests

I don't know if this is what you are looking for, Eric, but I still have the test setup ready if you want to request something else. I sort of forgot what the point of this was except to confirm our previous volume latency guesstimates...

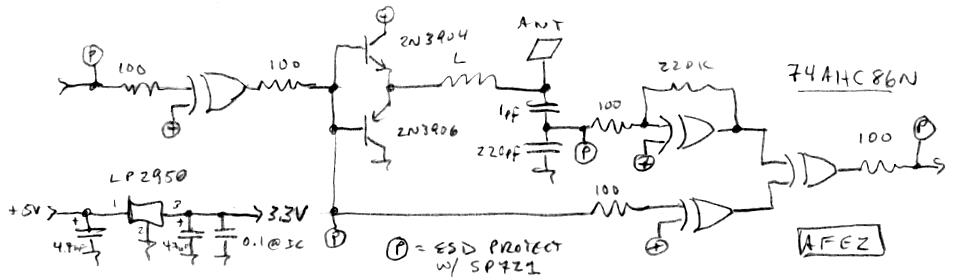

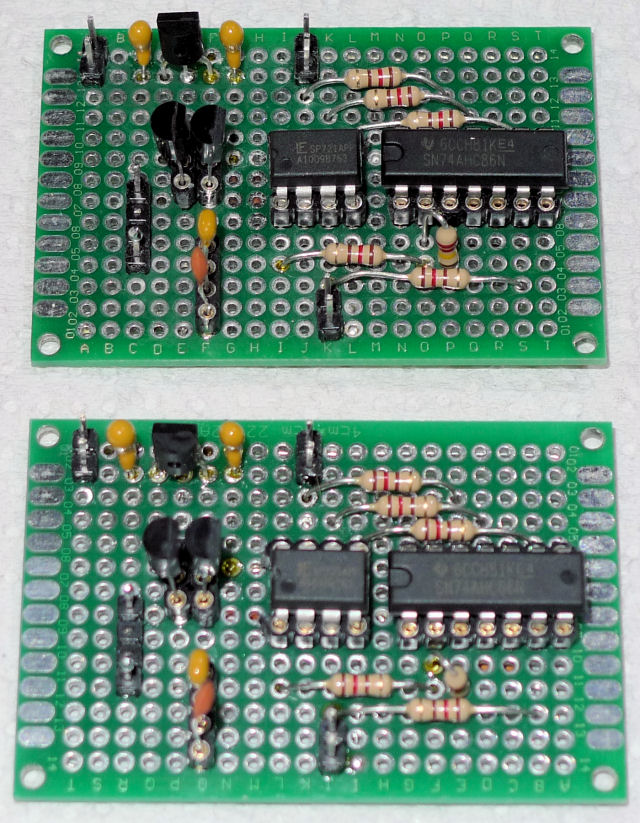

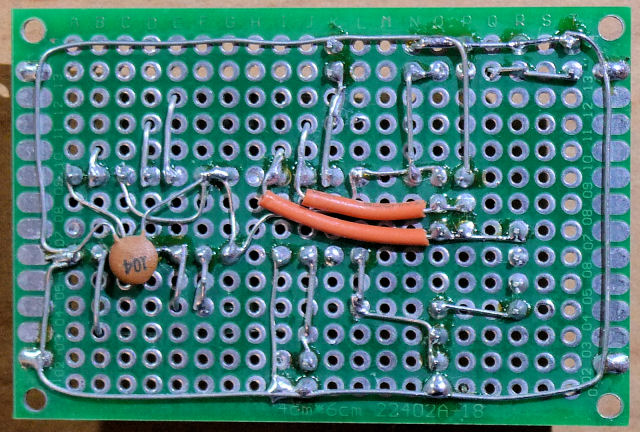

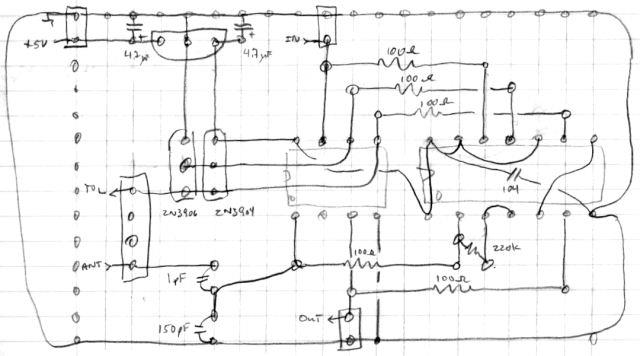

In order to simulate rapid hand movements on the pitch and volume antennas, I made a new board with a microwave relay that switched between two banks of pin sockets populated with paralleled fixed and/or variable capacitors. The D-Lev was calibrated with the normal antennas, then one antenna (whichever side was being tested) was removed and replaced by the relay switched to the minimum capacitance position. The capacitance for that side was adjusted to give nearly the same condition as with the normal antenna (either near-zero beat on the pitch or full-volume on the volume side). Then the relay was energized to switch in the larger capacitance, which was then also adjusted to simulate a near-hand raised pitch or reduced volume. This is different from the previous test in that this time an effort was made to select two switched capacitances that would give reasonable pitch or volume jumps (which turned out to be a little over an octave pitch, and about 36db volume).

Even without the antennas on the theremin this is a pretty twitchy test to run, and that's why my one-octave goal turned out to be 13 semitones, and the volume shift was set up to go from one fully lit volume LED to all four fully lit. The capacitance values are shown on the plots to be 1 and 3pf, but that only represents the values plugged into the test board. There were other parasitics and intentionally-placed metal objects near both the high- a low-capacitance sides of the test board to fine tune the two states.

I ran this using your FPGA load with the adjustable pitch and volume bandwidths, p_bw and v_bw. Before testing, I had been playing the theremin a bit and I wasn't sure that I could feel or hear any difference between the max and min pitch bandwidths, even with rapid trills. The volume bandwidth effect was of course a lot more noticeable.

Unfortunately I didn't have a better way of displaying pitch shift that I could overlay with the switching waveform, so these just show the sine wave and you have to look at the wave periods to imagine what the pitch response curve would look like. The first plot is the fastest pitch response with the bandwidth set to 4185. I would say this is within 10ms:

And this is the other extreme with the pitch bandwidth set to 16, resulting in something more like 40ms to settle out:

Even though it is difficult to see where the higher pitch actually settles out, I did notice that the p_vbw setting had no noticeable effect until I got down into the 300Hz range.

By accident I had some intermittent contact on one of the capacitor sockets for some time that was allowing a pitch jump of a little more than 3 octaves, and during this time running the bandwidth control from max to min resulted in a barely perceptible change in this larger pitch jump, with the 16Hz setting producing a very slight portamento tail. This was impressive because this represents a slew rate that is probably not humanly possible to achieve, and yet the pitch keeps up. My impression is that if you couldn't A-B compare the performance with between max and min bandwidths, you wouldn't be able to tell a difference while playing. The upside of keeping the pitch bandwidth low is that the extremely far field pitch noise is reduced, not so much because you hear it but because you can see it on the tuner.

The volume response tests were run the same way as the pitch tests, although the high and low capacitances were optimized to obtain a range that went from full volume to barely perceptible. Here of course it is much easier to see the response times. Plots for three bandwidths are shown; the two extremes of 16Hz and 4185Hz, and one at 202Hz where the volume response is clearly affected. There seemed to be no visible effect on latency until the bandwidth was reduced to about 550Hz.

Here are the three volume response plots at BW=4185Hz, 202Hz, and 16Hz:

With the volume bandwidth set anywhere in the range of 4185Hz down to 550Hz the full-amplitude volume latency stays within the golden 10ms limit. I don't know if there are any compelling reasons to limit the volume bandwidth, but I would like to see it kept as wide open as possible. I would think that the pitch bandwidth could be kept low, maybe even at 16Hz. Worst case, some fast trills might require a little more finger movement, but I don't really feel any sluggishness as you would with volume latency.

[EDIT] I'm going to take back those last two sentences. After playing some more with the pitch bandwidth set at both extremes it does seem that trills take a little more effort and are less responsive at v_bw=16. I tried increasing the bandwidth while watching for the setting where the far-field noise increases on the tuner, and the point at which trills become less inhibited unfortunately occurs where the noise filtering is minimal. If these bandwidth controls (or maybe just p_bw) could be left in permanently or at least for a while we may be able to come to a better answer on this.